ACTON, USA: MediaTek Inc., a leading fabless semiconductor company for wireless communications and digital media solutions, and Carbon Design Systems, the leading supplier of system level modeling and validation tools for system-on-chip (SoC) design, have entered into a multi-year strategic partnership to deploy Carbon Model Studio™ and Carbonized models of third-party intellectual property (IP) within Mediatek.

Over the past year, Mediatek engineers have successfully adopted Carbon’s system-level modeling to speedup electronic system level (ESL) platform buildup. During this time, architects adopted Carbon’s solutions for performance analysis and optimization of various subsystems in their advanced SoC designs.

Scott Seaton, vice president of sales and marketing at Carbon Design Systems, says: “This multi-year, strategic relationship between MediaTek and Carbon shows a deepening commitment by MediaTek to deploy system-level solutions to reduce time to market.

“It confirms our conviction that pre-built and pre-tested models of third-party IP and model generation tools are efficient to implement virtual platforms for architectural analysis/optimization and pre-silicon system validation.”

Saturday, October 31, 2009

Friday, October 30, 2009

MEMS-chip business struggles with growing pains

USA: The big, bright market potential of semiconductors built with microelectromechanical systems (MEMS) technology is indisputable. Annual sales of MEMS-based sensor and actuator devices are expected to nearly double in four years, reaching $7.3 billion in 2013, according to IC Insights' new Special Study: MEMS 2010—A Realistic Look Beyond the Hype.

However, it's erroneous to portray the burgeoning MEMS segment as a utopian market opportunity, says the 80+ page report, which reviews factors that have impaired MEMS sales growth in recent years and provides a detailed forecast of revenues, unit shipments, and average selling prices (ASPs) for sensor and actuator product categories through 2013.

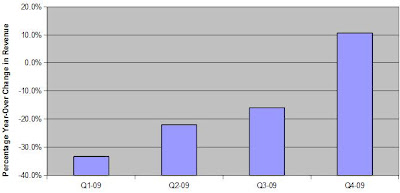

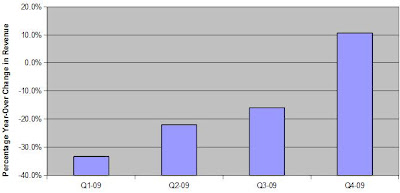

To be certain, 2009 was the first major setback for the MEMS-based semiconductor market since it began spreading into high-volume commercial systems applications from its traditional base in military/aerospace and automotive electronics.

IC Insights' new report shows worldwide sales of MEMS-based sensors and actuators falling 13 percent in 2009 to an estimated $3.8 billion from $4.4 billion in 2008. The drop is mostly due to the effects of the severe economic recession that pounded the entire semiconductor industry starting in 4Q08.

MEMS-based semiconductor sales are expected to rebound 17 percent in 2010 to $4.4 billion, followed by strong 21 percent and 22 percent increases in 2011 and 2012, respectively, according to the new report.

Fig. 1 ranks the sales performances of MEMS-product categories in 2009 and compares that to the report's projected 2008-2013 CAGR. The MEMS market overall is expected to increase by a CAGR of nearly 11% between 2008 and 2013 compared to a CAGR of just 6 percent for IC revenues, based on IC Insights' forecast.

Fig. 1 Source: IC Insights, USA

Source: IC Insights, USA

While the stage is set for strong increases in MEMS product sales during the next four years, it is important to recognize that this fledgling market segment remains vulnerable to periods of oversupply and price erosion—just like any other integrated circuit or discrete semiconductor category.

The new report shows that prior to 2009, the MEMS sensor/actuator segment suffered sales declines in two of the previous four years (in 2005 and 2007) strictly due to market/inventory corrections and steep price erosions in several key MEMS product categories.

These two down years for MEMS sales occurred when overall semiconductor revenues grew in 2005 and 2007. In recession-battered 2009, MEMS-based devices and ICs are expected to share equally in the pain of the semiconductor downturn with both markets forecast to decline 13 percent.

MEMS chip sales suffered greatly in 2009 because key automotive and new consumer applications have been hit especially hard by the global economic downturn.

IC Insights' 2010 MEMS report says the expanding MEMS market continues to face growing pains as suppliers attempt to serve new high-volume commercial systems applications. Ironically, a major challenge facing the MEMS semiconductor segment is the amount of attention and wafer-production capacity that's being heaped onto the business worldwide.

With traditional IC categories seeing a slowdown in annual growth rates since the late 1990s, more major semiconductor companies, pure-play IC foundries, and wafer fab equipment suppliers are shifting attention to the MEMS arena in order to boost revenues.

The entry of large device suppliers into market segments pioneered by MEMS start-up companies is radically changing the dynamics of many emerging niches. In many cases, the increased competition is intensifying pricing pressure in product categories that have promised substantial annual revenue growth rates.

Source: IC Insights

However, it's erroneous to portray the burgeoning MEMS segment as a utopian market opportunity, says the 80+ page report, which reviews factors that have impaired MEMS sales growth in recent years and provides a detailed forecast of revenues, unit shipments, and average selling prices (ASPs) for sensor and actuator product categories through 2013.

To be certain, 2009 was the first major setback for the MEMS-based semiconductor market since it began spreading into high-volume commercial systems applications from its traditional base in military/aerospace and automotive electronics.

IC Insights' new report shows worldwide sales of MEMS-based sensors and actuators falling 13 percent in 2009 to an estimated $3.8 billion from $4.4 billion in 2008. The drop is mostly due to the effects of the severe economic recession that pounded the entire semiconductor industry starting in 4Q08.

MEMS-based semiconductor sales are expected to rebound 17 percent in 2010 to $4.4 billion, followed by strong 21 percent and 22 percent increases in 2011 and 2012, respectively, according to the new report.

Fig. 1 ranks the sales performances of MEMS-product categories in 2009 and compares that to the report's projected 2008-2013 CAGR. The MEMS market overall is expected to increase by a CAGR of nearly 11% between 2008 and 2013 compared to a CAGR of just 6 percent for IC revenues, based on IC Insights' forecast.

Fig. 1

Source: IC Insights, USA

Source: IC Insights, USAWhile the stage is set for strong increases in MEMS product sales during the next four years, it is important to recognize that this fledgling market segment remains vulnerable to periods of oversupply and price erosion—just like any other integrated circuit or discrete semiconductor category.

The new report shows that prior to 2009, the MEMS sensor/actuator segment suffered sales declines in two of the previous four years (in 2005 and 2007) strictly due to market/inventory corrections and steep price erosions in several key MEMS product categories.

These two down years for MEMS sales occurred when overall semiconductor revenues grew in 2005 and 2007. In recession-battered 2009, MEMS-based devices and ICs are expected to share equally in the pain of the semiconductor downturn with both markets forecast to decline 13 percent.

MEMS chip sales suffered greatly in 2009 because key automotive and new consumer applications have been hit especially hard by the global economic downturn.

IC Insights' 2010 MEMS report says the expanding MEMS market continues to face growing pains as suppliers attempt to serve new high-volume commercial systems applications. Ironically, a major challenge facing the MEMS semiconductor segment is the amount of attention and wafer-production capacity that's being heaped onto the business worldwide.

With traditional IC categories seeing a slowdown in annual growth rates since the late 1990s, more major semiconductor companies, pure-play IC foundries, and wafer fab equipment suppliers are shifting attention to the MEMS arena in order to boost revenues.

The entry of large device suppliers into market segments pioneered by MEMS start-up companies is radically changing the dynamics of many emerging niches. In many cases, the increased competition is intensifying pricing pressure in product categories that have promised substantial annual revenue growth rates.

Source: IC Insights

Semiconductor opportunities in power grid applications

USA: Given the current urgency of rising energy costs, increased energy consumption, and climate change, it comes as little surprise that both the private and government sectors are increasing activities with regard to the energy grid, the so called electricity network supporting energy generation, transmission, and distribution.

Add to that, digital control for the infrastructure that monitors usage, the market opportunity is growing significantly for system providers as well as the component suppliers.

Energy grids in their current state are considered particularly inefficient, especially in the US, because arguably there are a large number of regulations and cost prohibitive roadblocks that have stalled its development over the last 40 years.

It’s a fact that a whopping 40 percent of all energy produced in the US is lost as heat as it travels over the wires to its final destination, while at the same time ever increasing power outages are costing the US roughly $150 billion annually.

As the demand for energy increases by an estimated 40 percent in the next 20 years according to some sources, it will become increasingly imperative that we recognize these issues and seek to solve them and in economic terms, this spells “opportunity” for electronics suppliers.

The technology industry has already addressed the smart metering segment of the electric power market and it continues to see success as the industry transitions into digital control through meter upgrades and new installations.

Companies such as Texas Instruments, STMicroelectronics, Microchip, and Teridian Semiconductor have been providing SOCs, AFEs, power, and microcontrollers into this growing application area.

Some 120 million smart meters are expected to ship this year, which provides an opportunity of $1.1B for silicon suppliers annually as there is just under $10.00 worth of silicon in each unit. These new meters go a long way in creating a more efficient grid by providing power companies with better data which can be used to regulate pricing during peak usage. They also provide the consumer with energy consumption information on power hungry appliances.

In addition, there is considerable room to improve the grid structure itself. As the new infrastructure build out continues for alternative sources of fuel outside of coal (solar, wind, and water), the grid is being retrofitted with additional systems such as PV arrays, PV inverters, programmable grid controllers, and simulation systems.

In the field, there is significant opportunity for electronics that will retrofit current transformers and switching substations with intelligent control and communications to be used as the infrastructure is decentralized due to the additional power generation coming online from micro-grids.

While the volumes are much lower on these applications, the silicon content is high and the required devices are priced much higher than those found in the AMR application.

Worldwide Semiconductor Revenue Forecast for AMR databeans estimates

databeans estimates

Source: Databeans

Add to that, digital control for the infrastructure that monitors usage, the market opportunity is growing significantly for system providers as well as the component suppliers.

Energy grids in their current state are considered particularly inefficient, especially in the US, because arguably there are a large number of regulations and cost prohibitive roadblocks that have stalled its development over the last 40 years.

It’s a fact that a whopping 40 percent of all energy produced in the US is lost as heat as it travels over the wires to its final destination, while at the same time ever increasing power outages are costing the US roughly $150 billion annually.

As the demand for energy increases by an estimated 40 percent in the next 20 years according to some sources, it will become increasingly imperative that we recognize these issues and seek to solve them and in economic terms, this spells “opportunity” for electronics suppliers.

The technology industry has already addressed the smart metering segment of the electric power market and it continues to see success as the industry transitions into digital control through meter upgrades and new installations.

Companies such as Texas Instruments, STMicroelectronics, Microchip, and Teridian Semiconductor have been providing SOCs, AFEs, power, and microcontrollers into this growing application area.

Some 120 million smart meters are expected to ship this year, which provides an opportunity of $1.1B for silicon suppliers annually as there is just under $10.00 worth of silicon in each unit. These new meters go a long way in creating a more efficient grid by providing power companies with better data which can be used to regulate pricing during peak usage. They also provide the consumer with energy consumption information on power hungry appliances.

In addition, there is considerable room to improve the grid structure itself. As the new infrastructure build out continues for alternative sources of fuel outside of coal (solar, wind, and water), the grid is being retrofitted with additional systems such as PV arrays, PV inverters, programmable grid controllers, and simulation systems.

In the field, there is significant opportunity for electronics that will retrofit current transformers and switching substations with intelligent control and communications to be used as the infrastructure is decentralized due to the additional power generation coming online from micro-grids.

While the volumes are much lower on these applications, the silicon content is high and the required devices are priced much higher than those found in the AMR application.

Worldwide Semiconductor Revenue Forecast for AMR

databeans estimates

databeans estimatesSource: Databeans

SMIC and Cadence announce 65nm low power reference flow 4.0

SAN JOSE, USA: Cadence Design Systems Inc. announced that it has delivered a comprehensive low-power design flow for engineers targeting the 65-nanometer process at Semiconductor Manufacturing International Corp..

Based on the Cadence(R) Low-Power Solution, the flow enables faster design of leading-edge, low-power semiconductors using a single, comprehensive design platform.

"Power is now a critical design constraint, as important as timing and area from both a technology and cost standpoint," said Max Liu, Vice President of the Design Services Center at SMIC. "The SMIC-Cadence Reference Flow 4.0 addresses the need for power-efficient design innovation with an advanced, automated low-power design capability."

Validation of the flow was accomplished through implementation of low-power chips utilizing SMIC's in-house-designed 65-nanometer libraries, including effective current source model (ECSM) standard cells, power management cells, PLLs, SRAMs and I/O libraries.

Low-power technologies employed in the design include power gating and multi-supply/multi-voltage (MSMV) techniques to reduce leakage and dynamic power consumption.

"Power efficiency is a key requirement for many new semiconductors, yet designers sometimes think it's too new and therefore too risky," said Steve Carlson, vice president of product marketing at Cadence. "The Cadence Low-Power Solution provides a complete, silicon-validated front-to-back flow for designers targeting SMIC's 65-nanometer process technology, including functional and structural verification, while increasing productivity. It's fast, easy and proven."

The SMIC 65-nanometer low-power Reference Flow 4.0 includes the Cadence Low-Power Solution, with Encounter Conformal Low Power, Incisive Enterprise Simulator, Encounter RTL Compiler, Encounter Digital Implementation System, Cadence QRC Extraction, Encounter Timing System and Encounter Power System.

Based on the Cadence(R) Low-Power Solution, the flow enables faster design of leading-edge, low-power semiconductors using a single, comprehensive design platform.

"Power is now a critical design constraint, as important as timing and area from both a technology and cost standpoint," said Max Liu, Vice President of the Design Services Center at SMIC. "The SMIC-Cadence Reference Flow 4.0 addresses the need for power-efficient design innovation with an advanced, automated low-power design capability."

Validation of the flow was accomplished through implementation of low-power chips utilizing SMIC's in-house-designed 65-nanometer libraries, including effective current source model (ECSM) standard cells, power management cells, PLLs, SRAMs and I/O libraries.

Low-power technologies employed in the design include power gating and multi-supply/multi-voltage (MSMV) techniques to reduce leakage and dynamic power consumption.

"Power efficiency is a key requirement for many new semiconductors, yet designers sometimes think it's too new and therefore too risky," said Steve Carlson, vice president of product marketing at Cadence. "The Cadence Low-Power Solution provides a complete, silicon-validated front-to-back flow for designers targeting SMIC's 65-nanometer process technology, including functional and structural verification, while increasing productivity. It's fast, easy and proven."

The SMIC 65-nanometer low-power Reference Flow 4.0 includes the Cadence Low-Power Solution, with Encounter Conformal Low Power, Incisive Enterprise Simulator, Encounter RTL Compiler, Encounter Digital Implementation System, Cadence QRC Extraction, Encounter Timing System and Encounter Power System.

ST's innovative SoC simplifies multimedia monitor design

GENEVA, SWITZERLAND: STMicroelectronics is the first to combine a DisplayPort 1.1a and HDMI 1.3 receiver to support full-high-definition sources, such as Blu-Ray, while providing comprehensive analog-video and audio connectivity.

The new STDP8028 SoC from ST simplifies the design of high-end Full-HD multimedia displays with its unique integration of video inputs, advanced video quality and usability features such as Picture-In-Picture (PIP) and Picture-By-Picture (PBP). The SoC is being designed into multi-function monitors and public displays by leading OEMs around the world.

While many chips targeting the multimedia monitor segment offer limited image-quality functions and interface choices, the STDP8028 delivers the highest functionality and comprehensive video-quality features, In addition, it also boasts the highest integration of various interfaces, making it suitable for large public-display monitors as well as superior-quality home audio/visual equipment.

The STDP8208 is DisplayPort 1.1a certified. DisplayPort, the open digital-interface standard for displays developed by VESA (Video Electronics Standards Association), enables high-bandwidth audio-video signal transmission using fewer signal lines than conventional display interfaces used in multimedia-monitor applications.

The device's integrated features include: multi-standard worldwide 3D video decoders for both standard- and high-definition inputs over CVBS, S-Video, and Component inputs; advanced Faroudja DCDi Cinema® technology to deliver high-performance; a high-quality video experience; and multi-standard digital audio decoders. In addition, the device's Game-Mode Support enables crisp graphics for gaming applications by maintaining less than one frame of delay.

Maximizing the value of its broad multimedia compatibility, the new SoC ensures high picture quality from various video sources by supporting Faroudja RealColor® technology and extended color gamut mapping support. Faroudja RealColor supports Adaptive Contrast Control II (ACC II) and Active Color Management-3D (ACM-3D), leading to exceptional video quality. This level of video quality technology, only previously seen on Faroudja Home Theater Systems, is now available in a single-chip solution.

Faroudja DCDi Cinema supports advanced format conversion up to 1080p resolution with pixel-based MADi (Motion Adaptive De-Interlacing). Implementing this MADi performance, the areas of an image that are not moving will be fully static (flicker free) and moving objects will have smooth edges.

The STDP8028 is in volume production and is available in a 409-ball HSBGA package.

The new STDP8028 SoC from ST simplifies the design of high-end Full-HD multimedia displays with its unique integration of video inputs, advanced video quality and usability features such as Picture-In-Picture (PIP) and Picture-By-Picture (PBP). The SoC is being designed into multi-function monitors and public displays by leading OEMs around the world.

While many chips targeting the multimedia monitor segment offer limited image-quality functions and interface choices, the STDP8028 delivers the highest functionality and comprehensive video-quality features, In addition, it also boasts the highest integration of various interfaces, making it suitable for large public-display monitors as well as superior-quality home audio/visual equipment.

The STDP8208 is DisplayPort 1.1a certified. DisplayPort, the open digital-interface standard for displays developed by VESA (Video Electronics Standards Association), enables high-bandwidth audio-video signal transmission using fewer signal lines than conventional display interfaces used in multimedia-monitor applications.

The device's integrated features include: multi-standard worldwide 3D video decoders for both standard- and high-definition inputs over CVBS, S-Video, and Component inputs; advanced Faroudja DCDi Cinema® technology to deliver high-performance; a high-quality video experience; and multi-standard digital audio decoders. In addition, the device's Game-Mode Support enables crisp graphics for gaming applications by maintaining less than one frame of delay.

Maximizing the value of its broad multimedia compatibility, the new SoC ensures high picture quality from various video sources by supporting Faroudja RealColor® technology and extended color gamut mapping support. Faroudja RealColor supports Adaptive Contrast Control II (ACC II) and Active Color Management-3D (ACM-3D), leading to exceptional video quality. This level of video quality technology, only previously seen on Faroudja Home Theater Systems, is now available in a single-chip solution.

Faroudja DCDi Cinema supports advanced format conversion up to 1080p resolution with pixel-based MADi (Motion Adaptive De-Interlacing). Implementing this MADi performance, the areas of an image that are not moving will be fully static (flicker free) and moving objects will have smooth edges.

The STDP8028 is in volume production and is available in a 409-ball HSBGA package.

TranSwitch ships over 1 million Mustang EPON ONU chips

SHELTON, USA: TranSwitch Corp. announced that it has shipped over 1 million chips from its Mustang product family, a class of Ethernet passive optical network (EPON) protocol system-on-chips (SoC) for optical networking unit (ONU) applications.

The Mustang devices provide the core functionality for the ONU equipment being deployed by Japan’s leading telecommunications service provider as part of its fiber-to-the-home (FTTH) strategy for offering triple-play (voice, internet and television) services.

“We are pleased to report this impressive milestone for our Mustang chips,” said Dr. Santanu Das, TranSwitch’s President and CEO. “The Mustang product family is integral to TranSwitch’s focus on offering a comprehensive platform of Access and Customer Premises Equipment (CPE) due to the high growth characteristics of this market segment. We look forward to leveraging our success in Japan as we accelerate the sales and marketing initiatives of our network edge products throughout Asia as well as other fast growing markets.”

The number of FTTH subscribers grew by 15 percent in the first six months of 2009, with more than 5.5 million new subscribers added worldwide, according to the latest update to the global ranking of FTTH economies, jointly issued by the three FTTH Councils of Asia-Pacific, Europe and North America.

According to industry analysts at ABI Research in their report PON and Active Ethernet FTTH Deployments, 55 percent percent of the world’s homes that will make their broadband connection over FTTH will receive video services by 2011. This figure is up from the 4 percent in 2005.

Japan and South Korea are ranked the highest in FTTH deployment, according to the report, with China possessing the greatest growth potential and one of the largest market opportunities. The build up of FTTH (and related deployments) in Europe has been growing with 120 new projects added in the last six months to a total of 233 projects at the end of June 2009, according to European telecom/IT consulting firm iDate.

Expanding TranSwitch’s end-to-end FTTH semiconductor portfolio, Mustang is a family of fully integrated, single chip, mixed-signal SoCs for gigabit EPON ONU applications.

This family of highly-integrated and low power EPON ONU SoCs is ideal for service providers deploying next generation networks (NGN) which support premium triple play services such as bandwidth-intensive IPTV while meeting government targets for reduced power consumption. These products enable new capabilities for television entertainment including interactivity, integration with voice and data communications, and value-added services while maintaining the highest quality of service.

The Mustang ONU simplifies service provider deployments by supporting interoperability with a variety of vendor optical line terminals (OLT) and supporting full compliance with relevant standards including IEEE 802.3ah and the NTT gigabit EPON Gist specification to ensure error-free, low latency, bandwidth efficient data transmission.

The Mustang product line, combined with TranSwitch’s Colt EPON OLT SoC and Atlanta 100 and 2000 communications processor families, reinforces TranSwitch’s market position as the only silicon vendor with complete, end-to-end EPON solutions for the “last mile.”

The Mustang devices provide the core functionality for the ONU equipment being deployed by Japan’s leading telecommunications service provider as part of its fiber-to-the-home (FTTH) strategy for offering triple-play (voice, internet and television) services.

“We are pleased to report this impressive milestone for our Mustang chips,” said Dr. Santanu Das, TranSwitch’s President and CEO. “The Mustang product family is integral to TranSwitch’s focus on offering a comprehensive platform of Access and Customer Premises Equipment (CPE) due to the high growth characteristics of this market segment. We look forward to leveraging our success in Japan as we accelerate the sales and marketing initiatives of our network edge products throughout Asia as well as other fast growing markets.”

The number of FTTH subscribers grew by 15 percent in the first six months of 2009, with more than 5.5 million new subscribers added worldwide, according to the latest update to the global ranking of FTTH economies, jointly issued by the three FTTH Councils of Asia-Pacific, Europe and North America.

According to industry analysts at ABI Research in their report PON and Active Ethernet FTTH Deployments, 55 percent percent of the world’s homes that will make their broadband connection over FTTH will receive video services by 2011. This figure is up from the 4 percent in 2005.

Japan and South Korea are ranked the highest in FTTH deployment, according to the report, with China possessing the greatest growth potential and one of the largest market opportunities. The build up of FTTH (and related deployments) in Europe has been growing with 120 new projects added in the last six months to a total of 233 projects at the end of June 2009, according to European telecom/IT consulting firm iDate.

Expanding TranSwitch’s end-to-end FTTH semiconductor portfolio, Mustang is a family of fully integrated, single chip, mixed-signal SoCs for gigabit EPON ONU applications.

This family of highly-integrated and low power EPON ONU SoCs is ideal for service providers deploying next generation networks (NGN) which support premium triple play services such as bandwidth-intensive IPTV while meeting government targets for reduced power consumption. These products enable new capabilities for television entertainment including interactivity, integration with voice and data communications, and value-added services while maintaining the highest quality of service.

The Mustang ONU simplifies service provider deployments by supporting interoperability with a variety of vendor optical line terminals (OLT) and supporting full compliance with relevant standards including IEEE 802.3ah and the NTT gigabit EPON Gist specification to ensure error-free, low latency, bandwidth efficient data transmission.

The Mustang product line, combined with TranSwitch’s Colt EPON OLT SoC and Atlanta 100 and 2000 communications processor families, reinforces TranSwitch’s market position as the only silicon vendor with complete, end-to-end EPON solutions for the “last mile.”

Juniper Networks unveils new silicon with breakthrough '3D Scaling' technology

NEW YORK, USA: Juniper Networks announced a new Junos One family of processors that represent an unprecedented integration of silicon and software to push the boundaries of high-performance networking.

The Junos One family combines Juniper’s experience and investments in silicon, software, systems and architecture to deliver industry-first “network instruction sets” that are purpose-built to meet the needs of networking at massive scale in multiple dimensions. Junos One chipsets will be embedded into a broad array of Juniper’s future routing, switching and security products.

Kicking off the new family, Juniper introduced the Junos Trio chipset with revolutionary 3D Scaling technology that enables networks to scale dynamically for more bandwidth, subscribers and services – all at the same time without compromise.

Junos Trio also yields breakthroughs for delivering rich business, residential and mobile services at massive scale – all while using half as much power per gigabit.i The new chipset includes more than 30 patent-pending innovations in silicon architecture, packet processing, quality of service and energy efficiency.

“Junos Trio with 3D Scaling is the only chipset of its kind on the planet,” said Pradeep Sindhu, Juniper’s founder, vice chairman and CTO. “We invested more than $80 million over the last five years to develop Junos Trio, yielding a fundamental advance in performance, flexibility and power efficiency to meet the Internet’s massive three-dimensional scaling needs. This will dramatically change the economics for our customers, while helping them create new and better experiences for their customers. This is the platform for the next decade.”

Junos Trio represents Juniper’s fourth generation of purpose-built silicon, and is the industry’s first “network instruction set” – a new silicon architecture unlike traditional application-specific integrated circuits (ASICs) and network processing units (NPUs).

The new architecture leverages customized “network instructions” that are designed into silicon to maximize performance and functionality, while working closely with Junos software to ensure programmability of network resources. The new Junos One family thus combines the performance benefits of ASICs and the flexibility of network processors to break the standard trade-offs between the two.

Built in 65-nanometer technology, Junos Trio includes four chips with a total of 1.5 billion transistors and 320 simultaneous processes, yielding total router throughput up to 2.6 terabits per second and up to 2.3 million subscribers per rackii – far exceeding the performance and scale possible through off-the-shelf silicon.

Junos Trio includes advanced forwarding, queuing, scheduling, synchronization and end-to-end resiliency features, helping customers provide service-level guarantees for voice, video, and data delivery. Junos Trio also incorporates significant power efficiency features to enable more environmentally conscious data center and service provider networks.

“From its start, Juniper has been a silicon technology leader with an impressive set of innovations through the years,” said Michael Howard, co-founder and principal analyst, Infonetics Research. “It is always exciting to see technology leaps such as those embedded in the Junos Trio chipset, which anticipates carrier edge and aggregation requirements across multiple dimensions for the next several years.”

Starting immediately, Junos Trio will be delivered in Juniper’s new MX 3D products that provide “universal edge” routing for business, residential and mobile services at massive scale on a single network. The new products include new modular line cards, new applications and new metro aggregation routers for Juniper’s MX Series routers.

The MX 3D products directly address enterprise and service provider needs for more flexible technology and business models, providing them with unprecedented dynamic control, open application platforms and revolutionary economics validated through a commissioned study conducted by an independent third party.

The Junos One family combines Juniper’s experience and investments in silicon, software, systems and architecture to deliver industry-first “network instruction sets” that are purpose-built to meet the needs of networking at massive scale in multiple dimensions. Junos One chipsets will be embedded into a broad array of Juniper’s future routing, switching and security products.

Kicking off the new family, Juniper introduced the Junos Trio chipset with revolutionary 3D Scaling technology that enables networks to scale dynamically for more bandwidth, subscribers and services – all at the same time without compromise.

Junos Trio also yields breakthroughs for delivering rich business, residential and mobile services at massive scale – all while using half as much power per gigabit.i The new chipset includes more than 30 patent-pending innovations in silicon architecture, packet processing, quality of service and energy efficiency.

“Junos Trio with 3D Scaling is the only chipset of its kind on the planet,” said Pradeep Sindhu, Juniper’s founder, vice chairman and CTO. “We invested more than $80 million over the last five years to develop Junos Trio, yielding a fundamental advance in performance, flexibility and power efficiency to meet the Internet’s massive three-dimensional scaling needs. This will dramatically change the economics for our customers, while helping them create new and better experiences for their customers. This is the platform for the next decade.”

Junos Trio represents Juniper’s fourth generation of purpose-built silicon, and is the industry’s first “network instruction set” – a new silicon architecture unlike traditional application-specific integrated circuits (ASICs) and network processing units (NPUs).

The new architecture leverages customized “network instructions” that are designed into silicon to maximize performance and functionality, while working closely with Junos software to ensure programmability of network resources. The new Junos One family thus combines the performance benefits of ASICs and the flexibility of network processors to break the standard trade-offs between the two.

Built in 65-nanometer technology, Junos Trio includes four chips with a total of 1.5 billion transistors and 320 simultaneous processes, yielding total router throughput up to 2.6 terabits per second and up to 2.3 million subscribers per rackii – far exceeding the performance and scale possible through off-the-shelf silicon.

Junos Trio includes advanced forwarding, queuing, scheduling, synchronization and end-to-end resiliency features, helping customers provide service-level guarantees for voice, video, and data delivery. Junos Trio also incorporates significant power efficiency features to enable more environmentally conscious data center and service provider networks.

“From its start, Juniper has been a silicon technology leader with an impressive set of innovations through the years,” said Michael Howard, co-founder and principal analyst, Infonetics Research. “It is always exciting to see technology leaps such as those embedded in the Junos Trio chipset, which anticipates carrier edge and aggregation requirements across multiple dimensions for the next several years.”

Starting immediately, Junos Trio will be delivered in Juniper’s new MX 3D products that provide “universal edge” routing for business, residential and mobile services at massive scale on a single network. The new products include new modular line cards, new applications and new metro aggregation routers for Juniper’s MX Series routers.

The MX 3D products directly address enterprise and service provider needs for more flexible technology and business models, providing them with unprecedented dynamic control, open application platforms and revolutionary economics validated through a commissioned study conducted by an independent third party.

Thursday, October 29, 2009

Tilera announces world's first 100-core processor with TILE-Gx family

SAN JOSE, USA: Tilera Corp. announced its new TILE-Gx family -- four new processors from Tilera including the world's first 100-core processor: the TILE-Gx100.

The TILE-Gx100 offers the highest performance of any microprocessor yet announced by a factor of four. Moreover, the entire TILE-Gx family raises the bar for performance-per-watt to new levels with ten times better compute efficiency compared to Intel's next generation Westmere processor.

And Tilera has simplified many-core programming with its breakthrough Multicore Development Environment (MDE) together with a growing ecosystem of operating system and software partners to enable rapid product deployment.

The TILE-Gx family -- available with 16, 36, 64 and 100 cores -- employs Tilera's unique architecture that scales well beyond the core count of traditional microprocessors.

Tilera's two-dimensional iMesh interconnect eliminates the need for an on-chip bus and its Dynamic Distributed Cache (DDC) system allows each cores' local cache to be shared coherently across the entire chip. These two key technologies enable the TILE Architecture performance to scale linearly with the number of cores on the chip -- a feat that is currently unmatched.

“"The launch of the TILE-Gx family, including the world's first 100-core microprocessor, ushers in a new era of many-core processing. We believe this next generation of high-core count, ultra high-performance chips will open completely new computing possibilities,” said Omid Tahernia, Tilera's CEO.

“Customers will be able to replace an entire board presently using a dozen or more chips with just one of our TILE-Gx processors, greatly simplifying the system architecture and resulting in reduced cost, power consumption, and PC board area. This is truly a remarkable technology achievement.”

Leading evolution to many-core

Tilera's breakthroughs in scalable multicore computing are changing the model of computing. Many-core processors enable a wide range of new opportunities including:

Consolidation of functions: A single many-core processor can absorb functions that previously required multiple processors, thus lowering system cost and providing a single software tool chain and programming model for developers.

Granularity of compute: Processing resources can be allocated to functions in precise increments, optimizing performance and saving power.

Deterministic compute: Enables processor cores to be dedicated to specific tasks, including cache-coherent islands of compute, for highly predictable performance.

“At various points in microprocessor history there have been breakthroughs that have enabled significant advances in computing, such as when the barrier of single-core clock speed was overcome by the introduction of multicore,” said Sergis Mushell, principal research analyst, Gartner.

“Cloud computing and virtualization have ushered in a new era of processing power optimization and utilization, which has accelerated the roadmaps for multicore architectures and changed the paradigm from a clock frequency discussion of the past to a new discussion about number of cores and core optimization.”

The TILE-Gx100 offers the highest performance of any microprocessor yet announced by a factor of four. Moreover, the entire TILE-Gx family raises the bar for performance-per-watt to new levels with ten times better compute efficiency compared to Intel's next generation Westmere processor.

And Tilera has simplified many-core programming with its breakthrough Multicore Development Environment (MDE) together with a growing ecosystem of operating system and software partners to enable rapid product deployment.

The TILE-Gx family -- available with 16, 36, 64 and 100 cores -- employs Tilera's unique architecture that scales well beyond the core count of traditional microprocessors.

Tilera's two-dimensional iMesh interconnect eliminates the need for an on-chip bus and its Dynamic Distributed Cache (DDC) system allows each cores' local cache to be shared coherently across the entire chip. These two key technologies enable the TILE Architecture performance to scale linearly with the number of cores on the chip -- a feat that is currently unmatched.

“"The launch of the TILE-Gx family, including the world's first 100-core microprocessor, ushers in a new era of many-core processing. We believe this next generation of high-core count, ultra high-performance chips will open completely new computing possibilities,” said Omid Tahernia, Tilera's CEO.

“Customers will be able to replace an entire board presently using a dozen or more chips with just one of our TILE-Gx processors, greatly simplifying the system architecture and resulting in reduced cost, power consumption, and PC board area. This is truly a remarkable technology achievement.”

Leading evolution to many-core

Tilera's breakthroughs in scalable multicore computing are changing the model of computing. Many-core processors enable a wide range of new opportunities including:

Consolidation of functions: A single many-core processor can absorb functions that previously required multiple processors, thus lowering system cost and providing a single software tool chain and programming model for developers.

Granularity of compute: Processing resources can be allocated to functions in precise increments, optimizing performance and saving power.

Deterministic compute: Enables processor cores to be dedicated to specific tasks, including cache-coherent islands of compute, for highly predictable performance.

“At various points in microprocessor history there have been breakthroughs that have enabled significant advances in computing, such as when the barrier of single-core clock speed was overcome by the introduction of multicore,” said Sergis Mushell, principal research analyst, Gartner.

“Cloud computing and virtualization have ushered in a new era of processing power optimization and utilization, which has accelerated the roadmaps for multicore architectures and changed the paradigm from a clock frequency discussion of the past to a new discussion about number of cores and core optimization.”

Synopsys unveils 30 percent smaller area, low power USB 2.0 PHY IP for 28-nm processes

MOUNTAIN VIEW, USA: Synopsys, Inc. (NASDAQ: SNPS), a world leader in software and IP for semiconductor design, verification and manufacturing, today announced the addition of the new DesignWare USB 2.0 picoPHY IP to its USB 2.0 PHY IP product line that has been successfully deployed in more than 300 customer designs, and in more than 50 different process technologies ranging from 180-nanometer (nm) to 32-nm.

Targeted at mobile and high-volume consumer applications such as feature-rich smartphones, mobile internet devices and netbooks, the DesignWare USB 2.0 picoPHY supports advanced 28-nm processes in a 1.8V architecture, is 30 percent smaller than the previous USB 2.0 PHY generation, and offers reduced pin count and low standby power consumption.

The DesignWare USB 2.0 picoPHY IP is the first PHY IP to support the new Battery Charging version 1.1 and USB On-the-Go (OTG) version 2.0 specifications from the USB Implementer's Forum (USB-IF).

The Battery Charging v 1.1 specification allows mobile devices to draw up to 1.8 A of current when connected to a wall charger. The Battery Charging specification enables portable devices to distinguish among various power sources, such as a wall charger, standard host port and USB charging port, and selects the most efficient method to charge the device.

By supporting the USB OTG version 2.0 specification, the DesignWare USB 2.0 picoPHY incorporates the new Attached Detection Protocol (ADP) feature, which improves the power efficiency of portable devices that communicate directly to USB peripherals without the need for a PC Host.

In addition, the DesignWare USB 2.0 picoPHY supports advanced power management features, such as power supply gating and support for ultra-low standby current to help designers lower the leakage power of mobile system-on-chips (SoCs) while maintaining the integrity of the USB 2.0 connection.

"Delivery of USB IP solutions from providers like Synopsys helps system designers benefit from the latest functionality offered by USB technology," said Jeff Ravencraft, president and chairman of the USB Implementers Forum.

"With the prevalence of USB on mobile devices, IP solutions like Synopsys' new DesignWare USB 2.0 picoPHY IP will enable designers to quickly incorporate this technology into their SoCs designs and bring new USB-enabled products to the market quickly."

"For nearly a decade, designers have successfully incorporated Synopsys' high-quality DesignWare USB 2.0 PHY IP into their SoCs which they have shipped in hundreds of millions of units," said John Koeter, vice president of marketing of the Solutions Group at Synopsys. "The addition of the new DesignWare USB 2.0 picoPHY IP to this already widely adopted product line provides designers with a competitive edge through our continued innovation and support for the latest processes and specifications."

The DesignWare USB 2.0 picoPHY IP is expected to be available to early adopters starting in Q4 2009 for 28-nm processes, with a roadmap for 40- and 32-nm.

Targeted at mobile and high-volume consumer applications such as feature-rich smartphones, mobile internet devices and netbooks, the DesignWare USB 2.0 picoPHY supports advanced 28-nm processes in a 1.8V architecture, is 30 percent smaller than the previous USB 2.0 PHY generation, and offers reduced pin count and low standby power consumption.

The DesignWare USB 2.0 picoPHY IP is the first PHY IP to support the new Battery Charging version 1.1 and USB On-the-Go (OTG) version 2.0 specifications from the USB Implementer's Forum (USB-IF).

The Battery Charging v 1.1 specification allows mobile devices to draw up to 1.8 A of current when connected to a wall charger. The Battery Charging specification enables portable devices to distinguish among various power sources, such as a wall charger, standard host port and USB charging port, and selects the most efficient method to charge the device.

By supporting the USB OTG version 2.0 specification, the DesignWare USB 2.0 picoPHY incorporates the new Attached Detection Protocol (ADP) feature, which improves the power efficiency of portable devices that communicate directly to USB peripherals without the need for a PC Host.

In addition, the DesignWare USB 2.0 picoPHY supports advanced power management features, such as power supply gating and support for ultra-low standby current to help designers lower the leakage power of mobile system-on-chips (SoCs) while maintaining the integrity of the USB 2.0 connection.

"Delivery of USB IP solutions from providers like Synopsys helps system designers benefit from the latest functionality offered by USB technology," said Jeff Ravencraft, president and chairman of the USB Implementers Forum.

"With the prevalence of USB on mobile devices, IP solutions like Synopsys' new DesignWare USB 2.0 picoPHY IP will enable designers to quickly incorporate this technology into their SoCs designs and bring new USB-enabled products to the market quickly."

"For nearly a decade, designers have successfully incorporated Synopsys' high-quality DesignWare USB 2.0 PHY IP into their SoCs which they have shipped in hundreds of millions of units," said John Koeter, vice president of marketing of the Solutions Group at Synopsys. "The addition of the new DesignWare USB 2.0 picoPHY IP to this already widely adopted product line provides designers with a competitive edge through our continued innovation and support for the latest processes and specifications."

The DesignWare USB 2.0 picoPHY IP is expected to be available to early adopters starting in Q4 2009 for 28-nm processes, with a roadmap for 40- and 32-nm.

Intel, Numonyx achieve research milestone with stacked, cross point phase change memory technology

SANTA CLARA, USA & GENEVA, SWITZERLAND: Intel Corp. and Numonyx B.V. today announced a key breakthrough in the research of phase change memory (PCM), a new non-volatile memory technology that combines many of the benefits of today's various memory types.

For the first time, researchers have demonstrated a 64Mb test chip that enables the ability to stack, or place, multiple layers of PCM arrays within a single die. These findings pave the way for building memory devices with greater capacity, lower power consumption and optimal space savings for random access non-volatile memory and storage applications.

The achievements are a result of an ongoing joint research program between Numonyx and Intel that has been focusing on the exploration of multi-layered or stacked PCM cell arrays.

Intel and Numonyx researchers are now able to demonstrate a vertically integrated memory cell -– called PCMS (phase change memory and switch). PCMS is comprised of one PCM element layered with a newly used Ovonic Threshold Switch (OTS) in a true cross point array.

The ability to layer or stack arrays of PCMS provides the scalability to higher memory densities while maintaining the performance characteristics of PCM, a challenge that is becoming increasingly more difficult to maintain with traditional memory technologies.

"We continue to develop the technology pipeline for memories in order to advance the computing platform,” said Al Fazio, Intel Fellow and director, memory technology development. “We are encouraged by this research milestone and see future memory technologies, such as PCMS, as critical for extending the role of memory in computing solutions and in expanding the capabilities for performance and memory scaling.”

"The results are extremely promising,” said Greg Atwood, senior technology fellow at Numonyx. “The results show the potential for higher density, scalable arrays and NAND-like usage models for PCM products in the future. This is important as traditional flash memory technologies face certain physical limits and reliability issues, yet demand for memory continues to rise in everything from mobile phones to data centers.”

Memory cells are built by stacking a storage element and a selector, with several cells creating memory arrays. Intel and Numonyx researchers were able to deploy a thin film, two-terminal OTS as the selector, matching the physical and electrical properties for PCM scaling.

With the compatibility of thin-film PCMS, multiple layers of cross point memory arrays are now possible. Once integrated together and embedded in a true cross point array, layered arrays are combined with CMOS circuits for decoding, sensing and logic functions.

For the first time, researchers have demonstrated a 64Mb test chip that enables the ability to stack, or place, multiple layers of PCM arrays within a single die. These findings pave the way for building memory devices with greater capacity, lower power consumption and optimal space savings for random access non-volatile memory and storage applications.

The achievements are a result of an ongoing joint research program between Numonyx and Intel that has been focusing on the exploration of multi-layered or stacked PCM cell arrays.

Intel and Numonyx researchers are now able to demonstrate a vertically integrated memory cell -– called PCMS (phase change memory and switch). PCMS is comprised of one PCM element layered with a newly used Ovonic Threshold Switch (OTS) in a true cross point array.

The ability to layer or stack arrays of PCMS provides the scalability to higher memory densities while maintaining the performance characteristics of PCM, a challenge that is becoming increasingly more difficult to maintain with traditional memory technologies.

"We continue to develop the technology pipeline for memories in order to advance the computing platform,” said Al Fazio, Intel Fellow and director, memory technology development. “We are encouraged by this research milestone and see future memory technologies, such as PCMS, as critical for extending the role of memory in computing solutions and in expanding the capabilities for performance and memory scaling.”

"The results are extremely promising,” said Greg Atwood, senior technology fellow at Numonyx. “The results show the potential for higher density, scalable arrays and NAND-like usage models for PCM products in the future. This is important as traditional flash memory technologies face certain physical limits and reliability issues, yet demand for memory continues to rise in everything from mobile phones to data centers.”

Memory cells are built by stacking a storage element and a selector, with several cells creating memory arrays. Intel and Numonyx researchers were able to deploy a thin film, two-terminal OTS as the selector, matching the physical and electrical properties for PCM scaling.

With the compatibility of thin-film PCMS, multiple layers of cross point memory arrays are now possible. Once integrated together and embedded in a true cross point array, layered arrays are combined with CMOS circuits for decoding, sensing and logic functions.

UMC invests 10 percent stake in DRAMeXchange

TAIWAN: Research institution DRAMeXchange announced that United Microelectronic Corp. (UMC) has taken a 10 percent stake in the company.

DRAMeXchange chairman Dr C.L. Liu believes that market intelligence has been gaining increasing attention nowadays and this investment through UMC's venture capital subsidiary is a true testament to this trend in the technology sector.

To stay ahead of the game and to seize new opportunities, industry players need to grasp the latest market dynamics and future trends. Dr. Liu added that, intelligence and culture are both intangible assets, which can be brought to their full potential through incisive analyses from various perspectives. For years, DRAMeXchange has successfully established its industry leader position and its high brand value by providing keen insights and reliable market information.

Unlike other Taiwan-based research institutions, 80 percent of DRAMeXchange’s revenue comes from analyses and strategic consulting it provides to leading global enterprises such as Goldman Sachs, Morgan Stanley, Bloomberg, Intel, Apple and Samsung.

DRAMeXchange was established in 2000, initially to provide DRAM market information and real-time quotes. Currently, there are four major research departments, namely, DRAMeXchange, WitsView, LEDinside and ENERGY, which are all leading research providers in their respective fields. Areas of research covered by DRAMeXchange are DRAM, NAND flash memory, PC, display panel, LED (light-emitting diodes), and the green energy.

Dr. Liu noted that DRAMeXchange is committed to providing crucial information to facilitate growth and internationalization of businesses in Taiwan.

UMC has been nurturing emerging enterprises that have the potential to internationalize, and DRAMeXchange is a vital intelligence provider for technology industries across the globe, it is also the first to profit among its competitors. After Taiwan witnessed the boom in the manufacturing and technology field, market intelligence and digital information will the next rising star.

In support of the government’s plans to carry out industry restructuring, and to promote the six key emerging industries, DRAMeXchange continues to innovate and to enhance the quality of its digital information. As a global leading brand, DRAMeXchange is slated to list on the OTC market in Taiwan’s bourse in the near future. Source: DRAMeXchange

Source: DRAMeXchange

DRAMeXchange chairman Dr C.L. Liu believes that market intelligence has been gaining increasing attention nowadays and this investment through UMC's venture capital subsidiary is a true testament to this trend in the technology sector.

To stay ahead of the game and to seize new opportunities, industry players need to grasp the latest market dynamics and future trends. Dr. Liu added that, intelligence and culture are both intangible assets, which can be brought to their full potential through incisive analyses from various perspectives. For years, DRAMeXchange has successfully established its industry leader position and its high brand value by providing keen insights and reliable market information.

Unlike other Taiwan-based research institutions, 80 percent of DRAMeXchange’s revenue comes from analyses and strategic consulting it provides to leading global enterprises such as Goldman Sachs, Morgan Stanley, Bloomberg, Intel, Apple and Samsung.

DRAMeXchange was established in 2000, initially to provide DRAM market information and real-time quotes. Currently, there are four major research departments, namely, DRAMeXchange, WitsView, LEDinside and ENERGY, which are all leading research providers in their respective fields. Areas of research covered by DRAMeXchange are DRAM, NAND flash memory, PC, display panel, LED (light-emitting diodes), and the green energy.

Dr. Liu noted that DRAMeXchange is committed to providing crucial information to facilitate growth and internationalization of businesses in Taiwan.

UMC has been nurturing emerging enterprises that have the potential to internationalize, and DRAMeXchange is a vital intelligence provider for technology industries across the globe, it is also the first to profit among its competitors. After Taiwan witnessed the boom in the manufacturing and technology field, market intelligence and digital information will the next rising star.

In support of the government’s plans to carry out industry restructuring, and to promote the six key emerging industries, DRAMeXchange continues to innovate and to enhance the quality of its digital information. As a global leading brand, DRAMeXchange is slated to list on the OTC market in Taiwan’s bourse in the near future.

Source: DRAMeXchange

Source: DRAMeXchange

Arasan and Cadence collaborate to extend verification best practices

SAN JOSE, USA: Arasan Chip Systems today announced an agreement with Cadence Design Systems to collaborate on delivering functional verification best practices.

Under the agreement, Cadence will engineer Arasan's MIPI design IP into the Cadence Incisive Verification Kit, which incorporates Cadence-developed MIPI-based verification IP, example flows, user workshops and documented best practices.

The collaboration will enable potential MIPI users to see first hand a comprehensive working environment with hands-on workshops and labs that demonstrate the industry-standard Open Verification Methodology (OVM). Cadence will distribute the kit as part of its Incisive verification solution.

Richard Timpa, Executive Vice President for Arasan Chip Systems, said: "We provide a complete suite to enable SOC designers to build their solution by way of IP cores, software drivers and verification/validation utilities.

"Many of our customers prefer the Cadence Incisive functional verification platform and the OVM-ready verification IP provided by Cadence to achieve the goals of first-time success with their SoC. This symbiotic relationship enables both Cadence and Arasan Chip Systems to provide the best possible solutions to our customers, "said .

Michal Siwinski, Group Marketing Director for Cadence Design Systems, added: "We see a major trend emerging around SoC integration, leveraging third-party design IP from companies like Arasan. This collaboration simplifies the challenge of verification at the SoC level, and offers a systematic approach to making sure that the protocol design IP can functionally connect and distribute transactions to devices supporting the protocol."

"Engineers can easily modify the pre-built executable verification plan to accommodate the particular configuration used in their integrated design and can add other elements from the Cadence Verification IP Portfolio of 30-plus protocols."

Further, Siwinski explained: "The Incisive Verification Kit effectively teaches these flows and use models by example, enabling our mutual customers to achieve significantly more complete verification results using the Incisive metric-driven verification techniques."

The integrated solution will be available with the Incisive Verification Kit, part of the Incisive Enterprise Simulator and Incisive Enterprise Verifier products, both of which are available now. The solution's initial focus is on the MIPI CSI protocol, but plans are in place to expand to MIPI DSI and USB 3.0, as well.

Under the agreement, Cadence will engineer Arasan's MIPI design IP into the Cadence Incisive Verification Kit, which incorporates Cadence-developed MIPI-based verification IP, example flows, user workshops and documented best practices.

The collaboration will enable potential MIPI users to see first hand a comprehensive working environment with hands-on workshops and labs that demonstrate the industry-standard Open Verification Methodology (OVM). Cadence will distribute the kit as part of its Incisive verification solution.

Richard Timpa, Executive Vice President for Arasan Chip Systems, said: "We provide a complete suite to enable SOC designers to build their solution by way of IP cores, software drivers and verification/validation utilities.

"Many of our customers prefer the Cadence Incisive functional verification platform and the OVM-ready verification IP provided by Cadence to achieve the goals of first-time success with their SoC. This symbiotic relationship enables both Cadence and Arasan Chip Systems to provide the best possible solutions to our customers, "said .

Michal Siwinski, Group Marketing Director for Cadence Design Systems, added: "We see a major trend emerging around SoC integration, leveraging third-party design IP from companies like Arasan. This collaboration simplifies the challenge of verification at the SoC level, and offers a systematic approach to making sure that the protocol design IP can functionally connect and distribute transactions to devices supporting the protocol."

"Engineers can easily modify the pre-built executable verification plan to accommodate the particular configuration used in their integrated design and can add other elements from the Cadence Verification IP Portfolio of 30-plus protocols."

Further, Siwinski explained: "The Incisive Verification Kit effectively teaches these flows and use models by example, enabling our mutual customers to achieve significantly more complete verification results using the Incisive metric-driven verification techniques."

The integrated solution will be available with the Incisive Verification Kit, part of the Incisive Enterprise Simulator and Incisive Enterprise Verifier products, both of which are available now. The solution's initial focus is on the MIPI CSI protocol, but plans are in place to expand to MIPI DSI and USB 3.0, as well.

CSR and TSMC collaboration reaches new milestones

BANGALORE, INDIA: CSR plc announced that it has shipped more than 1.5 billion units and processed more than one million wafers from foundry partner Taiwan Semiconductor Manufacturing Co.

CSR also announced that it is collaborating with TSMC on a leading edge 40nm low power (LP) RF process technology and that CSR has validated a broad range of proprietary connectivity IP blocks at this node for incorporation into their next generation Connectivity Centre SoCs.

As the pioneer in bringing single die Bluetooth products on RFCMOS technology, CSR has worked closely with TSMC over multiple generations of technologies and delivered a broad range of innovative products to mainstream consumer markets. CSR has shipped more than 1.5 billion products that drive connectivity across multiple markets including mobile phones, automobiles, computers and consumer electronics devices.

CSR's Connectivity Centre SoCs require a small form factor and lower power consumption to deliver seamless connectivity for next-generation wireless devices.

TSMC’s 40nm LP RF process technology enables CSR to meet these objectives with highly integrated multi radio devices that allow the seamless coexistence of Bluetooth, GPS, Wi-Fi and FM radios. The two companies are leveraging their long relationship to help CSR achieve 40nm leadership with its multifunction radio integrated silicon platforms.

“TSMC consistently delivers cutting edge technology platforms that include integrated design collaterals and ecosystems. Our 40nm platform supports the high performance, low power, and high density RF products that will help CSR deliver next-generation experiences,” said Mark Liu, Vice President of Advanced Technology Business at TSMC.

“CSR is a demonstrated wireless technology leader because of their unique ability to bring these news experiences to reality.”

“CSR’s close collaboration with TSMC is key to our ability to deliver significant

advantages to our customers through industry-leading integration, power efficiency and cost efficiency of our products. We enable our customers to do more for less by selecting the technology nodes appropriate for the platform architecture we are delivering,” said Mark Redford, Vice President Advanced Process Technology Development of CSR.

“CSR’s highly integrated designs, with its portfolio of technology node optimized proprietary IP blocks, bring the best connectivity experience possible to wireless users worldwide.”

CSR also announced that it is collaborating with TSMC on a leading edge 40nm low power (LP) RF process technology and that CSR has validated a broad range of proprietary connectivity IP blocks at this node for incorporation into their next generation Connectivity Centre SoCs.

As the pioneer in bringing single die Bluetooth products on RFCMOS technology, CSR has worked closely with TSMC over multiple generations of technologies and delivered a broad range of innovative products to mainstream consumer markets. CSR has shipped more than 1.5 billion products that drive connectivity across multiple markets including mobile phones, automobiles, computers and consumer electronics devices.

CSR's Connectivity Centre SoCs require a small form factor and lower power consumption to deliver seamless connectivity for next-generation wireless devices.

TSMC’s 40nm LP RF process technology enables CSR to meet these objectives with highly integrated multi radio devices that allow the seamless coexistence of Bluetooth, GPS, Wi-Fi and FM radios. The two companies are leveraging their long relationship to help CSR achieve 40nm leadership with its multifunction radio integrated silicon platforms.

“TSMC consistently delivers cutting edge technology platforms that include integrated design collaterals and ecosystems. Our 40nm platform supports the high performance, low power, and high density RF products that will help CSR deliver next-generation experiences,” said Mark Liu, Vice President of Advanced Technology Business at TSMC.

“CSR is a demonstrated wireless technology leader because of their unique ability to bring these news experiences to reality.”

“CSR’s close collaboration with TSMC is key to our ability to deliver significant

advantages to our customers through industry-leading integration, power efficiency and cost efficiency of our products. We enable our customers to do more for less by selecting the technology nodes appropriate for the platform architecture we are delivering,” said Mark Redford, Vice President Advanced Process Technology Development of CSR.

“CSR’s highly integrated designs, with its portfolio of technology node optimized proprietary IP blocks, bring the best connectivity experience possible to wireless users worldwide.”

FormFactor unveils next-generation 300mm full-wafer test solution for NAND flash

LIVERMORE, USA: FormFactor Inc. has unveiled the TouchMatrix probe solution -- its latest-generation 300-mm full-wafer contact probe card for NAND Flash devices. Built on a new, proprietary architecture that leverages FormFactor's MicroSpring MEMS contact technology, the TouchMatrix solution offers chip manufacturers superior product performance with a substantially reduced production lead time.

The TouchMatrix probe card is specifically designed for today's cost sensitive test flows and enables testing of Flash devices down to sub 32-nm process nodes, including those integrating three-bit and four-bit memory cell architectures.

"While under enormous manufacturing cost pressures, Flash memory manufacturers must test each device to ensure its functional performance and quality," stated Adrian Wilson, general manager of the Flash Business Unit at FormFactor.

"Our Flash customers need innovative solutions that can lower their cost of test and this was the focus and goal of our TouchMatrix solution. Cost and performance are equally important to them. Our TouchMatrix solution provides superior electrical and probe contact performance, and its new architecture also has the benefit of manufacturing efficiency, which allows us to pass savings along to our customers."

As Flash memory devices migrate to the 32-nm node and employ smaller, multi-level cell architectures, increasing noise and crosstalk can affect test signals, making the role of the interconnect between the wafer and tester ever-more critical.

TouchMatrix cards utilize FormFactor's proprietary MicroSpring technology which provides low noise and stable contact resistance -- enabling reliable testing of smaller Flash device architectures and ensuring high test yield.

The MicroSpring contacts are manufactured using semiconductor lithography processes, making them highly scalable to Flash manufacturers' roadmaps as they migrate to smaller device features. FormFactor's self-cleaning MEMS probe tips also require less maintenance -- further extending test uptime and improving test cell efficiency.

The TouchMatrix solution features an innovative architecture that significantly improves manufacturing efficiency and reduces the delivery lead time for the TouchMatrix probe card, allowing customers greater flexibility in determining the type and volume of product to ramp at a given time.

The TouchMatrix architecture does not require the full wafer map to initiate production, which means manufacturing can begin as early as first silicon. Probe card repair is also made easier since the card can be easily disassembled and reassembled without planarity or x/y position adjustments.

The TouchMatrix probe card is designed for improved thermal performance that enables it to quickly reach and maintain test temperatures -- improving throughput and extending uptime. The card can also be enhanced with FormFactor's patented RapidSoak technology to achieve near-zero soak time and superior scrub performance.

FormFactor's TouchMatrix probe cards are now in qualification testing at several Flash device manufacturers and are available for shipping.

The TouchMatrix probe card is specifically designed for today's cost sensitive test flows and enables testing of Flash devices down to sub 32-nm process nodes, including those integrating three-bit and four-bit memory cell architectures.

"While under enormous manufacturing cost pressures, Flash memory manufacturers must test each device to ensure its functional performance and quality," stated Adrian Wilson, general manager of the Flash Business Unit at FormFactor.

"Our Flash customers need innovative solutions that can lower their cost of test and this was the focus and goal of our TouchMatrix solution. Cost and performance are equally important to them. Our TouchMatrix solution provides superior electrical and probe contact performance, and its new architecture also has the benefit of manufacturing efficiency, which allows us to pass savings along to our customers."

As Flash memory devices migrate to the 32-nm node and employ smaller, multi-level cell architectures, increasing noise and crosstalk can affect test signals, making the role of the interconnect between the wafer and tester ever-more critical.

TouchMatrix cards utilize FormFactor's proprietary MicroSpring technology which provides low noise and stable contact resistance -- enabling reliable testing of smaller Flash device architectures and ensuring high test yield.

The MicroSpring contacts are manufactured using semiconductor lithography processes, making them highly scalable to Flash manufacturers' roadmaps as they migrate to smaller device features. FormFactor's self-cleaning MEMS probe tips also require less maintenance -- further extending test uptime and improving test cell efficiency.

The TouchMatrix solution features an innovative architecture that significantly improves manufacturing efficiency and reduces the delivery lead time for the TouchMatrix probe card, allowing customers greater flexibility in determining the type and volume of product to ramp at a given time.

The TouchMatrix architecture does not require the full wafer map to initiate production, which means manufacturing can begin as early as first silicon. Probe card repair is also made easier since the card can be easily disassembled and reassembled without planarity or x/y position adjustments.

The TouchMatrix probe card is designed for improved thermal performance that enables it to quickly reach and maintain test temperatures -- improving throughput and extending uptime. The card can also be enhanced with FormFactor's patented RapidSoak technology to achieve near-zero soak time and superior scrub performance.

FormFactor's TouchMatrix probe cards are now in qualification testing at several Flash device manufacturers and are available for shipping.

Intersil and Georgia Institute of Technology in joint alliance for high-performance semiconductor development

MILPITAS & ATLANTA, USA: Intersil Corp., a world leader in the design and manufacture of high-performance analog and mixed-signal semiconductors, announced a broad alliance with the Georgia Institute of Technology.

The announcement includes the opening of a major new development facility and the kickoff of several new programs dedicated to the research and development of advanced power management semiconductor technologies.

This unique alliance involves an on-campus Analog Processing Center of Excellence (ACE) and world-class research efforts across multiple Georgia Tech facilities. A keystone of the alliance will be the opening of a new 4,300 square-foot ACE Center on campus. At the Georgia Electronic Design Center (GEDC), Intersil engineers, along with Georgia Tech students and faculty, will focus on creating advanced power management circuit designs.

Intersil and the Institute will also engage in joint development through a strategic alliance on advanced process technology development for semiconductors used in high-voltage power management and distribution. The new center will also utilize a technique developed at a Georgia Tech-founded company known as collaborative signal processing that removes performance-limiting impairments such as signal loss, dispersion, skew and noise.

This initiative is expected to spawn significant power savings in the electrical grid and tomorrow's data centers. The partnership is built on Intersil's longstanding leadership as an expert in the development of power management technologies and recent research advances in semiconductor fabrication processes.

"The clean and efficient generation, transmission and storage of power are key challenges of the twenty-first century," said Dave Bell, CEO, Intersil. "Intersil is delighted to be working closely with one of the world's finest educational institutions to develop innovative technologies that will meet our needs for smarter, greener and more efficient power solutions."

As energy costs soar and greenhouse gases accumulate, there is an increasing need for higher-voltage, higher-performance semiconductor technologies for power grids worldwide. Intersil and Georgia Tech are creating a strategic alliance to co-develop high-voltage power management circuits using breakthrough process technologies. In addition, Intersil will fund two graduate fellowships in electrical engineering.

"Georgia Tech's partnership with Intersil is an ideal example of academic and industrial leaders joining forces to co-develop advanced real-world technologies," said Georgia Tech President G.P. 'Bud' Peterson. "Working together, we will develop sustainable energy solutions and create jobs."

The new Analog Processing Center of Excellence (ACE) is a spinout of the Georgia Electronic Design Center and is located in the Centergy One building in Technology Square on the Georgia Tech campus. The facility already employs eight engineers who use state-of-the-art computer-aided design (CAD) tools to do complex analog systems simulation.